# Systems and Devices 1 Lec 3a : Combinatorial Logic

### Before we get started ...

- We live in the fourth generation of computers:

- ► Thermionic value, Transistor, IC, Micro-processor

- Default technology: transistor, therefore preferred number base: binary, processed using Boolean logic gate.

- How do we process data within our computer?

- Identify the state of the computer e.g. what operation it is currently performing, what data has been selected to be processed and what results are produced?

Slide 1

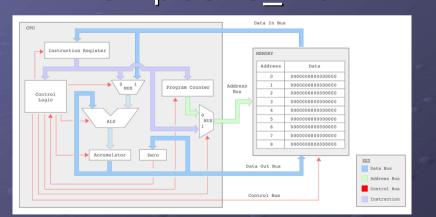

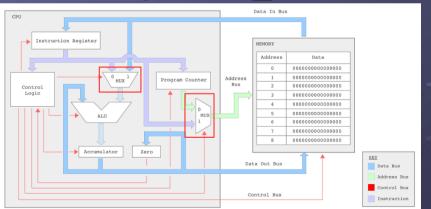

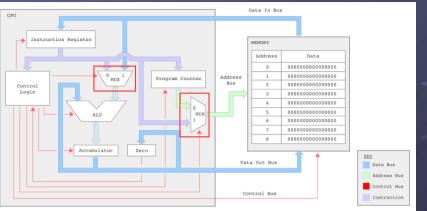

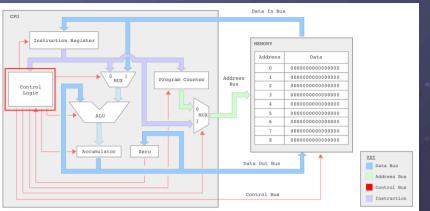

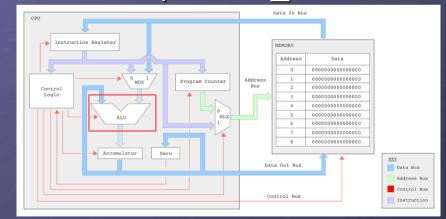

# SimpleCPU v1a

University of York : M Freeman 2021

#### Block diagram

We need to implement each functional block using logic gates i.e. as combinatorial logic circuits. University of York : M Freeman 2021

# SimpleCPU\_v1a

Block diagram

Slide 2

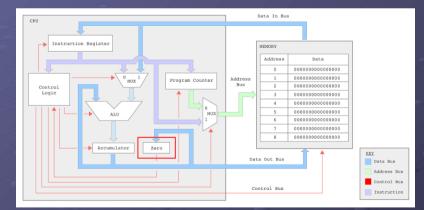

Status bits : to control the flow of information in a computer we need to test its state i.e. data values. University of York : M Freeman 2021

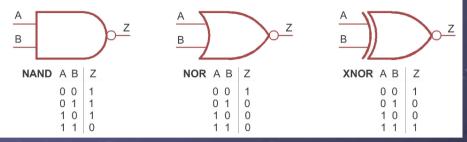

### Logic gates

- Quick quizzz: what logic gate could be used to test if :

- Two bits are equal

- Two bits are both zero

- At least one bit is zero

A = B = 0 A = 0 OR B = 0

A = B

University of York : M Freeman 2021

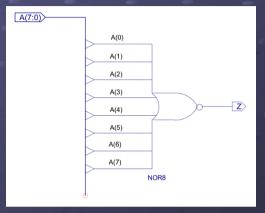

# Example : NOR\_8.zip

To test if an 8 bit value is zero we can use an 8 bit NOR gate.

Slide 6

ilide 8

University of York : M Freeman 2021

Slide 7

Slide 5

# SimpleCPU\_v1a

#### Block diagram

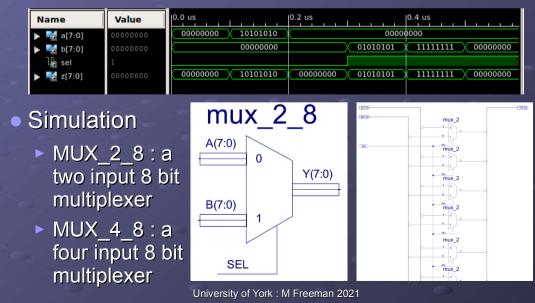

Multiplexer : a core requirement of any computer is to route / move data between functional blocks. University of York : M Freeman 2021

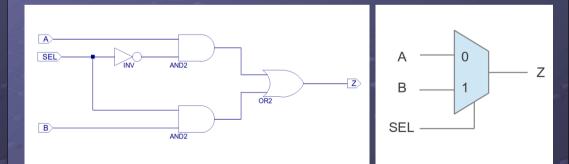

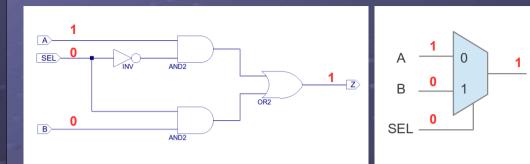

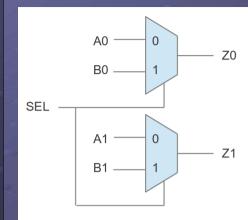

#### **Multiplexers**

#### • 2:1 1bit data multiplexer (MUX)

- Gate level implementation and Circuit Symbol

- IF SEL = 0 THEN Z = A

- ► IF SEL = 1 THEN Z = B

University of York : M Freeman 2021

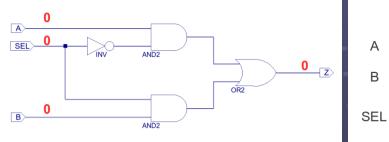

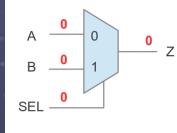

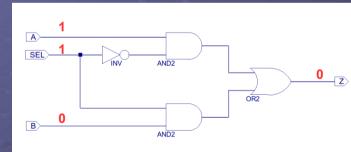

# **Multiplexers**

- 2:1 1bit data multiplexer (MUX)

- Gate level implementation and Circuit Symbol

- ► IF SEL = 0 THEN Z = A

- ► IF SEL = 1 THEN Z = B

University of York : M Freeman 2021

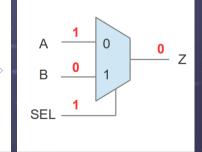

### **Multiplexers**

Ζ

- 2:1 1bit data multiplexer (MUX)

- Gate level implementation and Circuit Symbol

- ► IF SEL = 0 THEN Z = A

- ► IF SEL = 1 THEN Z = B

University of York : M Freeman 2021

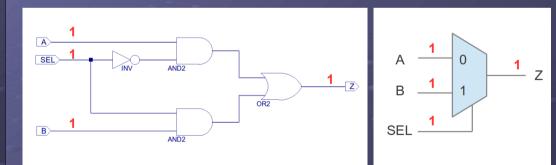

# **Multiplexers**

#### • 2:1 1bit data multiplexer (MUX)

- Gate level implementation and Circuit Symbol

- ► IF SEL = 0 THEN Z = A

- ► IF SEL = 1 THEN Z = B

### **Multiplexers**

#### • 2:1 1bit data multiplexer (MUX)

- Gate level implementation and Circuit Symbol

- IF SEL = 0 THEN Z = A

- ► IF SEL = 1 THEN Z = B

# SimpleCPU\_v1a

- Problem : the two highlighted multiplexers need to select between two 8 bit values.

- May also need to select between more than two input sources.

University of York : M Freeman 2021

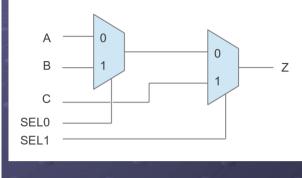

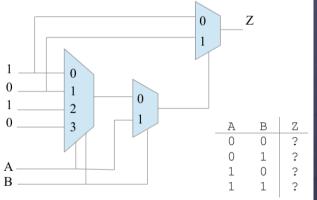

# **Multiplexers**

2:1 x 2bit MUX: Parallel MUX to increase width

3:1 x 1bit MUX: Serial MUX to increase inputs

Slide 15

• Quick quiz: complete the truth table

Bonus question : what two logic gates can be used to implement this circuit?

University of York : M Freeman 2021

## University of York : M Freeman 2021

Slide 16

Slide 14

# Example : MUX\_2.zip

# SimpleCPU\_v1a

#### • Block diagram

Encoders / Decoders : within the processor information is stored using a range of binary representations.

University of York : M Freeman 2021

#### **Binary encoding**

Slide 18

| Decimal | Binary    | BCD       | One-hot             |

|---------|-----------|-----------|---------------------|

| 0       | 0000 0000 | 0000 0000 | 0000 0000 0000 0001 |

| 1       | 0000 0001 | 0000 0001 | 0000 0000 0000 0010 |

| 2       | 0000 0010 | 0000 0010 | 0000 0000 0000 0100 |

| 3       | 0000 0011 | 0000 0011 | 0000 0000 0000 1000 |

| 4       | 0000 0100 | 0000 0100 | 0000 0000 0001 0000 |

| 5       | 0000 0101 | 0000 0101 | 0000 0000 0010 0000 |

| 6       | 0000 0110 | 0000 0110 | 0000 0000 0100 0000 |

| 7       | 0000 0111 | 0000 0111 | 0000 0000 1000 0000 |

| 8       | 0000 1000 | 0000 1000 | 0000 0001 0000 0000 |

| 9       | 0000 1001 | 0000 1001 | 0000 0010 0000 0000 |

| 10      | 0000 1010 | 0001 0000 | 0000 0100 0000 0000 |

| 11      | 0000 1011 | 0001 0001 | 0000 1000 0000 0000 |

| 12      | 0000 1100 | 0001 0010 | 0001 0000 0000 0000 |

| 13      | 0000 1101 | 0001 0011 | 0010 0000 0000 0000 |

| 14      | 0000 1110 | 0001 0100 | 0100 0000 0000 0000 |

| 15      | 0000 1111 | 0001 0101 | 1000 0000 0000 0000 |

Alternative binary representations : Binary Coded Decimal (BCD) and One-hot encoding. University of York : M Freeman 2021

Slide 19

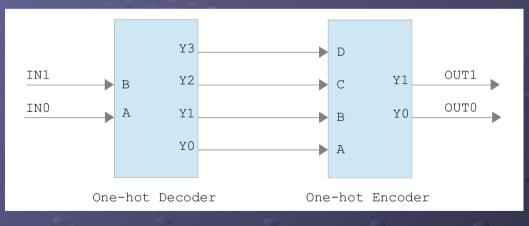

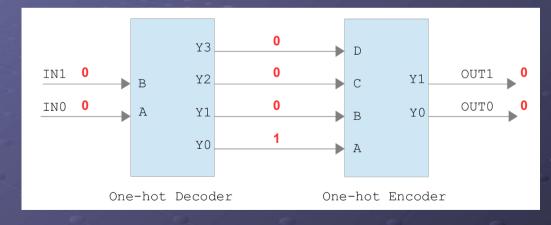

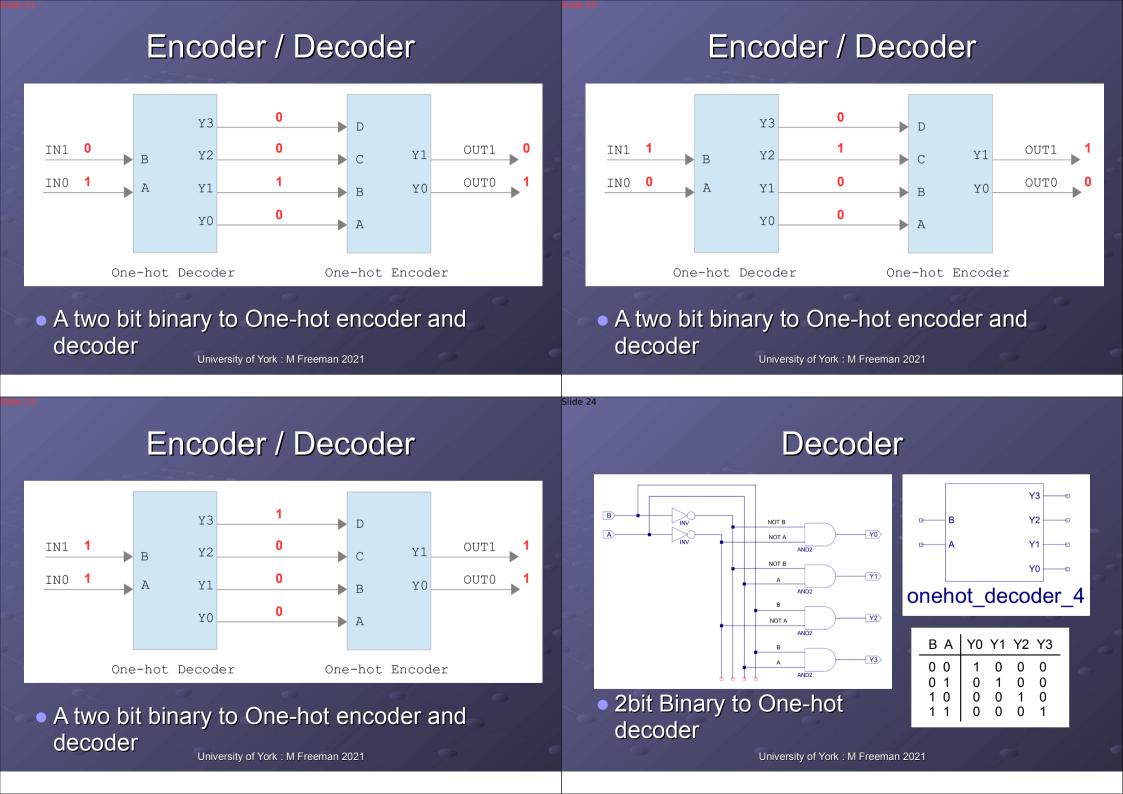

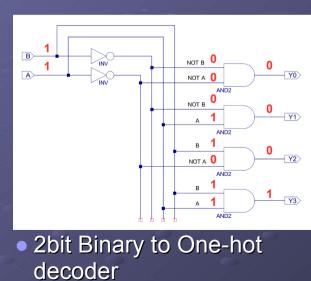

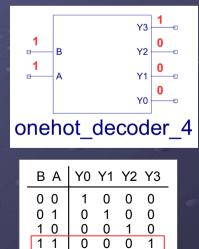

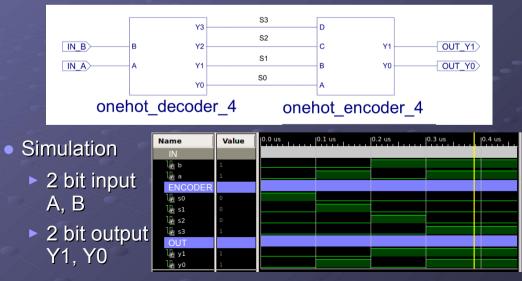

### Encoder / Decoder

# A two bit binary to One-hot encoder and decoder

University of York : M Freeman 2021

# Encoder / Decoder

• A two bit binary to One-hot encoder and decoder

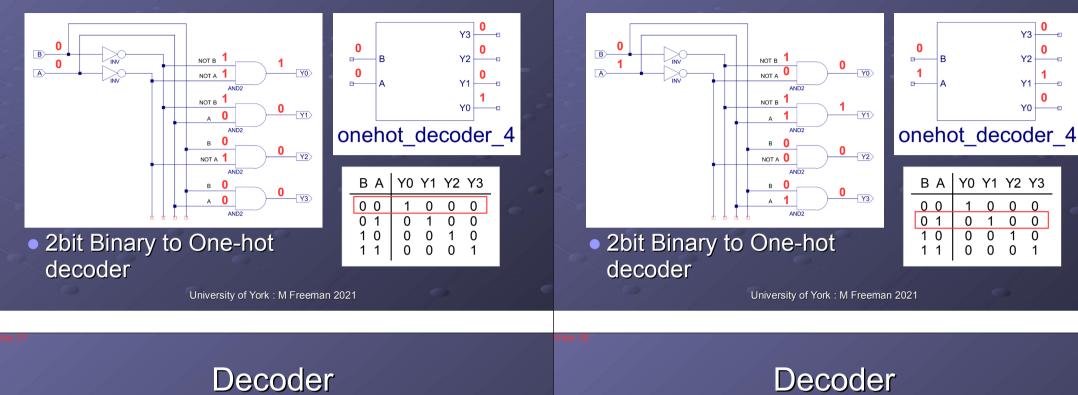

#### Decoder

#### Decoder

0

decoder

0

0

Y3

Y2

Y1

Y0

0 0

0

1 0 0

0 1 0

0 0 1

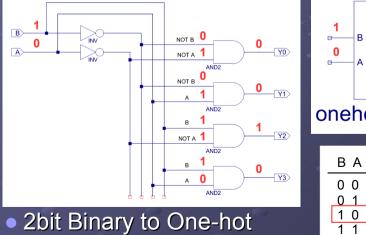

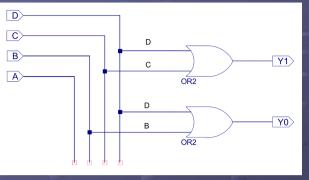

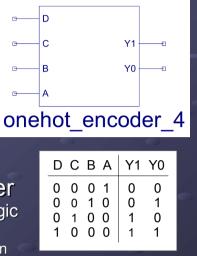

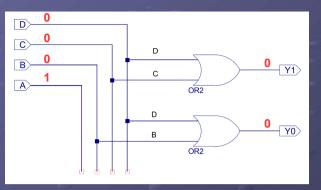

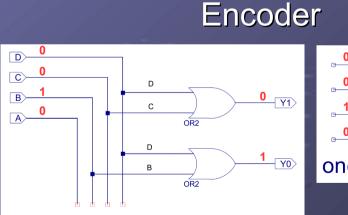

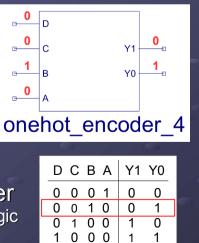

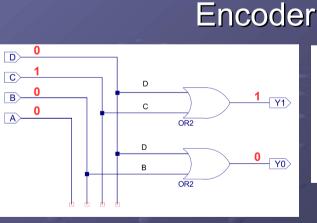

# Encoder

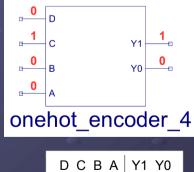

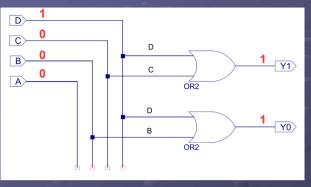

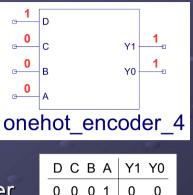

#### 2bit One-hot to Binary encoder

- One-hot representation simplifies logic design i.e. only 1 bit is ever set.

- Identify when output is a logic 1 then join active inputs with OR gates.

University of York : M Freeman 2021

### Encoder

#### 2bit One-hot to Binary encoder

- One-hot representation simplifies logic design i.e. only 1 bit is ever set.

- Identify when output is a logic 1 then join active inputs with OR gates.

University of York : M Freeman 2021

| 0<br>0<br>1 | C<br>B<br>A |   |   |    | Y1<br>Y0 | 0   |   |

|-------------|-------------|---|---|----|----------|-----|---|

| one         | ho          | t | e | าต | od       | er_ | 4 |

|             | D           | С | В | А  | Y1       | Y0  | 1 |

| er          | 0           | 0 | 0 | 1  | 0        | 0   |   |

| gic         | 0           | 0 | 1 | 0  | 0        | 1   |   |

| yic         | 0           | 1 | 0 | 0  | 1        | 0   |   |

|             | 1           | 0 | 0 | 0  | 1        | 1   |   |

• D

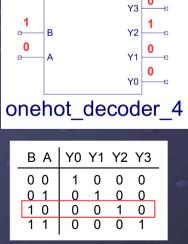

#### 2bit One-hot to Binary encoder

- One-hot representation simplifies logic design i.e. only 1 bit is ever set.

- Identify when output is a logic 1 then join active inputs with OR gates.

University of York : M Freeman 2021

#### 2bit One-hot to Binary encoder

- One-hot representation simplifies logic design i.e. only 1 bit is ever set.

- Identify when output is a logic 1 then join active inputs with OR gates.

|   | C | В | А | Ϋ́ | ΥĽ |

|---|---|---|---|----|----|

| 0 | 0 | 0 | 1 | 0  | 0  |

| 0 | 0 | 1 | 0 | 0  | 1  |

| 0 | 1 | 0 | 0 | 1  | 0  |

| 1 | 0 | 0 | 0 | 1  | 1  |

University of York : M Freeman 2021

## Encoder

0 0 1 0

0 1 0 0

1 0 0 0

0 1

1

1 1

0

#### 2bit One-hot to Binary encoder

- One-hot representation simplifies logic design i.e. only 1 bit is ever set.

- Identify when output is a logic 1 then join active inputs with OR gates.

University of York : M Freeman 2021

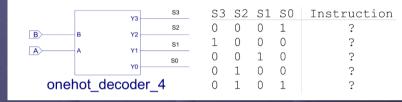

### Encoder / Decoder

Which of the following is a valid one-hot value?A) 00000000B) 01000000C) 10000010

An instruction is represented within a computer by a two bit binary number:

$\begin{array}{cc} A B \\ 0 1 = Add \end{array} \qquad \begin{array}{c} A B \\ 0 0 = Subtract \end{array}$

Slide 34

Slide 36

1 0 = Multiply 1 1 = Divide

This two bit code is decoded using the onehot\_decoder\_4 component to produce control signals S0, S1, S2 and S3. Complete tge truth table below, identifying what instruction is being processed.

Quick quizzz

University of York : M Freeman 2021

Slide 35

# Example : onehot\_encoder.zip

SimpleCPU\_v1a

Block diagram

ALU : a core requirement of any computer is to process data i.e. the Arithmetic and Logic unit, at its heart is the ADDER.

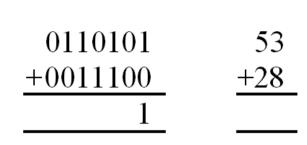

# Key skills : working in base 2 Ke

Slide 38

Slide 40

Adding two binary numbers : 53 + 28

Positive, integer

University of York : M Freeman 2021

# Key skills : working in base 2

| 53  |

|-----|

| +28 |

|     |

|     |

Adding two binary numbers : 53 + 28

Positive, integer

University of York : M Freeman 2021

Slide 37

### Key skills : working in base 2

| 0110101 + 0011100 | 53<br>+28 |

|-------------------|-----------|

| 001               | 120       |

| 1                 |           |

Adding two binary numbers : 53 + 28

Positive, integer

University of York : M Freeman 2021

# Key skills : working in base 2

| 0110101  | 53  |

|----------|-----|

| +0011100 | +28 |

| 0001     |     |

| 11       |     |

Adding two binary numbers : 53 + 28

Positive, integer

University of York : M Freeman 2021

# Key skills : working in base 2

| 0110101  | 53                                      |

|----------|-----------------------------------------|

| +0011100 | +28                                     |

| 10001    | <i>2</i> 2                              |

| 111      | ~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~ |

Adding two binary numbers : 53 + 28

Positive, integer

University of York : M Freeman 2021

# Key skills : working in base 2

Slide 42

lide 44

| 0110101  | 53  |

|----------|-----|

| +0011100 | +28 |

| 010001   |     |

| 1111     |     |

|          |     |

Adding two binary numbers : 53 + 28

Positive, integer

University of York : M Freeman 2021

Slide 43

# Key skills : working in base 2

| 0110101  | 53  |

|----------|-----|

| +0011100 | +28 |

| 1010001  | 81  |

| 1111     |     |

Adding two binary numbers : 53 + 28

Positive, integer

University of York : M Freeman 2021

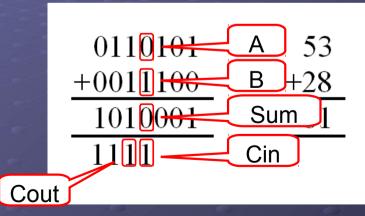

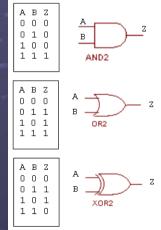

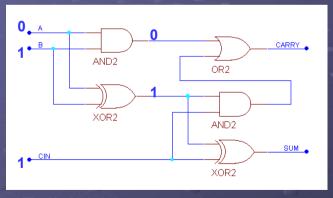

# **Binary addition**

Adding two binary numbers : 53 + 28

Positive, integer

University of York : M Freeman 2021

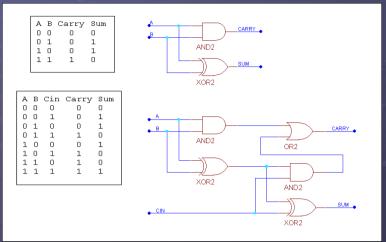

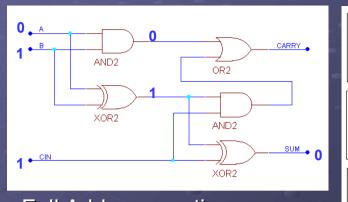

# **Binary addition**

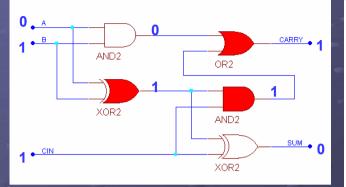

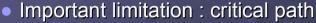

#### Half and full adder

Basic components can be combined into larger circuits University of York : M Freeman 2021

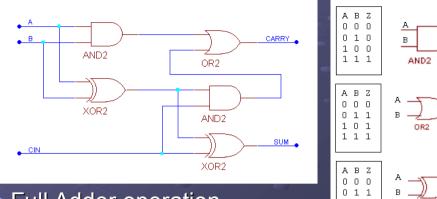

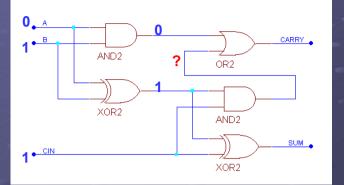

## **Binary addition**

Full Adder operation

Slide 46

University of York : M Freeman 2021

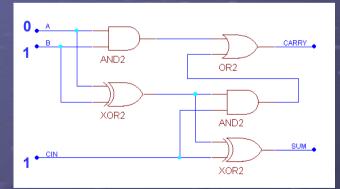

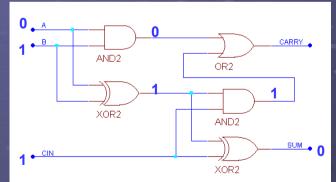

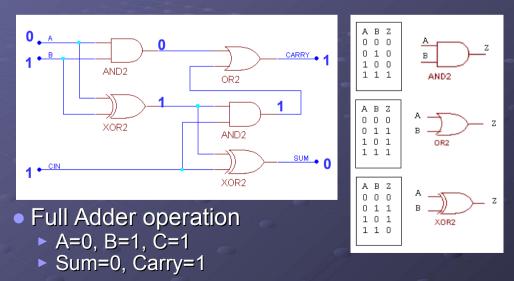

# **Binary addition**

Full Adder operation ► A=0, B=1, C=1

# **Binary addition**

Full Adder operation

Update outputs with stable values

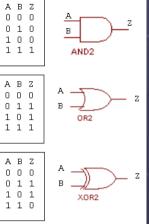

## Binary addition

Full Adder operation

If input not known, trace signal back to source

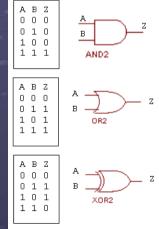

АВΖ

Full Adder operation

Update outputs with stable values

University of York : M Freeman 2021

## **Binary addition**

University of York : M Freeman 2021

Full Adder operation

Update outputs with stable values

### **Binary addition**

University of York : M Freeman 2021

University of York : M Freeman 2021

# Binary addition

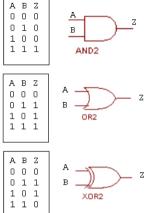

Worst case delay path, a signal needs to travel through three gate to produce a stable output. University of York : M Freeman 2021

#### **Binary addition**

Quick Quizzz

Slide 54

Which rank these circuits in order of critical path delay, quickest to slowest.

University of York : M Freeman 2021

Slide 55

# Summary

- Key concepts :

- Fundamental building blocks of a computer:

- Multiplexer (bit and byte), Encoder, Decoder, Adder ...

- Binary encodings

- Binary, BCD, One-hot, Gray code ...

- Link : https://en.wikipedia.org/wiki/Gray\_code

- Binary arithmetic

- Half adder, Full adder, Ripple adder, Carry, Overflow.

- Hardware limitations : Critical Path Delay (CPD)

- Each logic gate will take some time to update its output for a change on its input i.e. propagation delay.

- Operation of simple combinatorial logic circuits