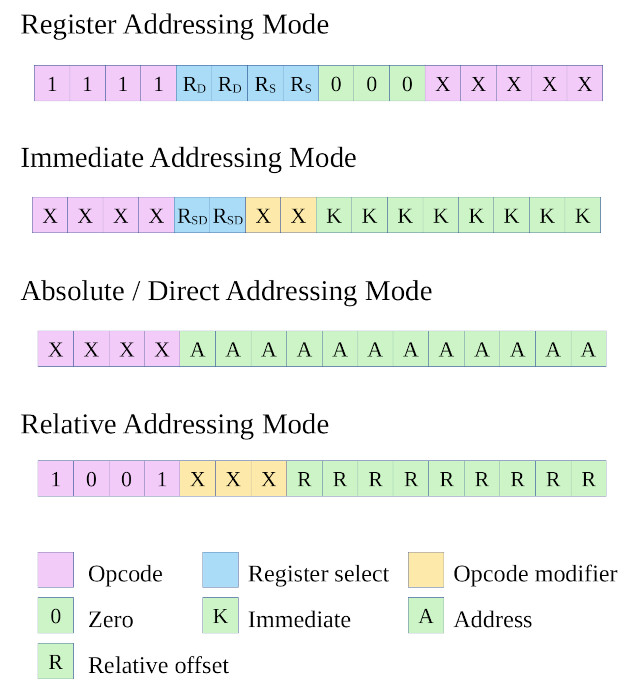

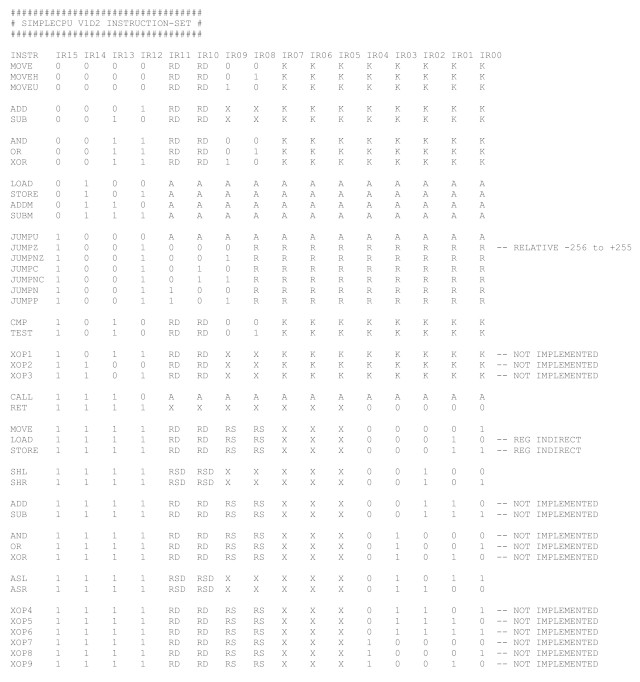

Example : sub RC 33 Addressing mode : immediate Opcode : 0010 XX RTL : RX <- RX - ( (K7)8 || KK ) Flags set : Z,C,O,P,N

Subtract signed 8bit value from general purpose register. The bit field KK is as defined in figure 2. In this example RX is register RC and KK is the value 3, signed extended to 16bits. Therefore, if RC=5 at the end of the execution phase register RC=2.

And

Example : and RD 4 Addressing mode : immediate Opcode : 0011 00 RTL : RX <- RX & ( (0)8 || KK ) Flags set : Z,C,O,P,N

Perform 8bit bitwise AND on general purpose register. The bit field KK is as defined in figure 2. In this example RX is register RD and KK is the value 4. Therefore, if RD=7 at the end of the execution phase register RD=4. Note, as the value KK represents a binary pattern this data is not sign extended.

Or

Example : or RD 4 Addressing mode : immediate Opcode : 0011 01 RTL : RX <- RX & ( (0)8 || KK ) Flags set : Z,C,O,P,N

Perform 8bit bitwise OR on general purpose register. The bit field KK is as defined in figure 2. In this example RX is register RD and KK is the value 4. Therefore, if RD=3 at the end of the execution phase register RD=7. Note, as the value KK represents a binary pattern this data is not sign extended.

Xor

Example : xor RD 4 Addressing mode : immediate Opcode : 0011 10 RTL : RX <- RX & ( (0)8 || KK ) Flags set : Z,C,O,P,N

Perform 8bit bitwise AND on general purpose register. The bit field KK is as defined in figure 2. In this example RX is register RD and KK is the value 4. Therefore, if RD=7 at the end of the execution phase register RD=3. Note, as the value KK represents a binary pattern this data is not sign extended.

Load

Example : load RA 123 Addressing mode : absolute Opcode : 0100 RTL : RA <- M[AAA] Flags set : None

Transfer a 16bit value from memory to general purpose register RA. The bit field AAA is as defined in figure 2. In this example AAA is the address 123, therefore, if M[123]=10 at the end of the execution phase register RA=10. Note, the destination register is hardwired to register RA, you can not use other registers.

Store

Example : store RA 234 Addressing mode : absolute Opcode : 0101 RTL : M[AAA] <- RA Flags set : None

Store 16bit value in general purpose register RA to memory. The bit field AAA is as defined in figure 2. In this example AAA is the address 234, therefore, if RA=9 at the end of the execution phase memory location M[234]=9. Note, the source register is hardwired to register RA, you can not use other registers.

Addm

Example : addm RA 345 Addressing mode : absolute Opcode : 0110 RTL : RA <- RA + M[AAA] Flags set : Z,C,O,P,N

Add 16bit value stored in memory to general purpose register RA. The bit field AAA is as defined in figure 2. In this example AAA is the address 345, therefore, if RA=20 and M[345]=10 at the end of the execution phase register RA=30. Note, the destination register is hardwired to register RA, you can not use other registers.

Subm

Example : subm RA 456 Addressing mode : absolute Opcode : 0111 RTL : RA <- RA - M[AAA] Flags set : Z,C,O,P,N

Subtract 16bit value stored in memory from general purpose register RA. The bit field AAA is as defined in figure 2. In this example AAA is the address 456, therefore, if RA=20 and M[456]=10 at the end of the execution phase register RA=10. Note, the destination register is hardwired to register RA, you can not use other registers.

Jumpu or Jump

Example : jump 200 Addressing mode : direct Opcode : 1000 RTL : PC <- AAA Flags set : None

Unconditional jump. The bit field AAA is as defined in figure 2. In this example AAA is the address 200, at the end of the execution phase the PC is updated to 200.

Jumpz

Example : jumpz 201 Addressing mode : direct Opcode : 1001 000 RTL : IF Z=1 THEN PC <- AAA ELSE PC <- PC + 1 Flags set : None

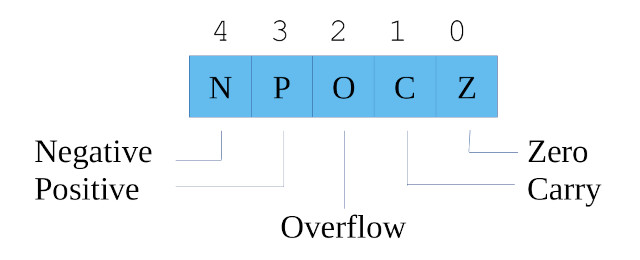

Jump if last arithmetic or logical instruction produced a zero result i.e. jump is conditional on the status register’s Z flag. The bit field AAA is as defined in figure 2. In this example AAA is the address 201, if Z=1 the PC is set to the value 201 at the end of the execution phase, else PC+1. Note, status register (Z flag) is only updated by arithmetic or logical functions.

Jumpnz

Example : jumpnz 202 Addressing mode : direct Opcode : 1001 001 RTL : IF Z=0 THEN PC <- AAA ELSE PC <- PC + 1 Flags set : None

Jump if last arithmetic or logic instruction did not produce a zero result i.e. jump is conditional on the status register’s Z flag. The bit field AAA is as defined in figure 2. In this example AAA is the address 202, if Z=0 the PC is set to the value 202 at the end of the execution phase, else PC+1. Note, status register (Z flag) is only updated by arithmetic or logical functions.

Jumpc

Example : jumpc 203 Addressing mode : direct Opcode : 1001 010 RTL : IF C=1 THEN PC <- AAA ELSE PC <- PC + 1 Flags set : None

Jump if last arithmetic instruction generated a carry i.e. jump is conditional on the status register’s C flag. The bit field AAA is as defined in figure 2. In this example AAA is the address 203, if C=1 the PC is set to the value 203 at the end of the execution phase, else PC+1. Note, status register (C flag) is only updated by arithmetic functions.

Jumpnc

Example : jumpnc 203 Addressing mode : direct Opcode : 1001 011 RTL : IF C=0 THEN PC <- AAA ELSE PC <- PC + 1 Flags set : None

Jump if last arithmetic instruction generated a carry i.e. jump is conditional on the status register’s C flag. The bit field AAA is as defined in figure 2. In this example AAA is the address 203, if C=0 the PC is set to the value 203 at the end of the execution phase, else PC+1. Note, status register (C flag) is only updated by arithmetic functions.

Jumpn

Example : jumpn 203 Addressing mode : direct Opcode : 1001 100 RTL : IF N=1 THEN PC <- AAA ELSE PC <- PC + 1 Flags set : None

Jump if last arithmetic instruction generated a negative result i.e. jump is conditional on the status register’s N flag. The bit field AAA is as defined in figure 2. In this example AAA is the address 203, if N=1 the PC is set to the value 203 at the end of the execution phase, else PC+1. Note, status register (N flag) is only updated by arithmetic functions.

Jumpp

Example : jumpc 203 Addressing mode : direct Opcode : 1011 RTL : IF P=1 THEN PC <- AAA ELSE PC <- PC + 1 Flags set : None

Jump if last arithmetic instruction generated a positive result i.e. jump is conditional on the status register’s P flag. The bit field AAA is as defined in figure 2. In this example AAA is the address 203, if P=1 the PC is set to the value 203 at the end of the execution phase, else PC+1. Note, status register (P flag) is only updated by arithmetic functions.

Example : cmp RC 33 Addressing mode : immediate Opcode : 1010 00 RTL : RX - ( (K7)8 || KK ) Flags set : Z,C,O,P,N

Subtract signed 8bit value from general purpose register. The bit field KK is as defined in figure 2. In this example RX is register RC and KK is the value 33, signed extended to 16bits. Therefore, if RC=5 at the end of the execution phase register RC=5, Z=0, C=0, P=0, N=1.

Test

Example : test RD 4 Addressing mode : immediate Opcode : 1010 01 RTL : RX & ( (0)8 || KK ) Flags set : Z,C,O,P,N

Perform 8bit bitwise AND on general purpose register. The bit field KK is as defined in figure 2. In this example RX is register RD and KK is the value 4. Therefore, if RD=7 at the end of the execution phase register RD=7, Z=0, C=0, P=1, N=0. Note, as the value KK represents a binary pattern this data is not sign extended.

Call

Example : call 300

Addressing mode : direct

Opcode : 1110

RTL : STACK[SP]<- PC + 1

: SP <- SP + 1

: PC <- AAA

Flags set : None

Call subroutine. The bit field AAA is as defined in figure 2. In this example AAA is the address 300, at the end of the execution phase the PC is updated to 300. Note, CALL-RET stack memory is implemented in a separate memory space i.e. LIFO buffer, with integrated stack pointer (SP), max depth of 4.

Ret

Example : ret

Addressing mode : direct

Opcode : 1111 + 00000

RTL : SP <- SP - 1

: PC <- STACK[SP]

Flags set : None

Return from subroutine. At the end of the execution phase the PC will be updated to the value on the top of the CALL-RET stack. Note, CALL-RET stack memory is implemented in a separate memory space i.e. LIFO buffer, with integrated stack pointer (SP), max depth of 4.

Move

Example : move ra rb Addressing mode : register Opcode : 1111 + 00001 RTL : RX <- RY Flags set : None

Transfer a 16bit value from source to destination general purpose register. Higher and lower opcode values as defined in figure 2. In this example RX is register RA and RY is register RB, therefore, if RB=1 and RA=100 at the end of the execution phase register RA=1.

Load

Example : load ra (rb) Addressing mode : register indirect Opcode : 1111 + 00010 RTL : RX <- M[RY] Flags set : None

Transfer a 16bit value from memory to destination general purpose register. Accessed memory address stored in register enclosed by brackets. Higher and lower opcode values as defined in figure 2. In this example RX is register RA and RY is register RB, therefore, if RB=100 and M[100]=5 at the end of the execution phase register RA=5.

Store

Example : store rb (rc) Addressing mode : register indirect Opcode : 1111 + 00011 RTL : M[RY] <- RX Flags set : None

Transfer a 16bit value from general purpose register to memory. Accessed memory address stored in register enclosed by brackets. Higher and lower opcode values as defined in figure 2. In this example RX is register RB and RY is register RC, therefore, if RB=10 and RC=100 at the end of the execution phase memory location M[100]=10.

shl

Example : shl rb

Addressing mode : register

Opcode : 1111 + 00100

RTL : RX <- ( RX(14:0) || C )

: C <- RX(15)

Flags set : Z,C,O,P,N

Shift bits within general purpose register one position to the left, carry flag moved into LSB. MSB moved into C flag. Higher and lower opcode values as defined in figure 2. In this example RX is register RB, therefore, if RB=2 and C=1, at the end of the execution phase register RB=5, C=0.

shr

Example : shr rb

Addressing mode : register

Opcode : 1111 + 00101

RTL : RX <- ( C || RX(15:1) )

: C <- RX(0)

Flags set : Z,C,O,P,N

Shift bits within general purpose register one position to the right, carry flag moved into MSB. LSB moved into C flag. Higher and lower opcode values as defined in figure 2. In this example RX is register RB, therefore, if RB=2 and C=1, at the end of the execution phase register RB=0x8001.

asl

Example : asl rb

Addressing mode : register

Opcode : 1111 + 01011

RTL : RX <- ( RX(14:0) || 0 )

: C <- RX(15)

Flags set : Z,C,O,P,N

Shft bits within general purpose register one position to the left, 0 moved into LSB. MSB moved into C flag. Higher and lower opcode values as defined in figure 2. In this example RX is register RB, therefore, if RB=2 at the end of the execution phase register RB=4 and C=0.

asr

Example : asr rb

Addressing mode : register

Opcode : 1111 + 0100

RTL : RX <- ( 0 || RX(15:1) )

: C <- RX(0)

Flags set : Z,C,O,P,N

Rotate bits within general purpose register one position to the right, 0 moved into MSB. LSB moved into C flag. Higher and lower opcode values as defined in figure 2. In this example RX is register RB, therefore, if RB=3 at the end of the execution phase register RB=1 and C=1

IMPORTANT: the instructions below have not been implemented in the base simpleCPUv1d system. However, these instruction can be added to the system if required.

Xop1

Example : xop1 rb 1 Addressing mode : immediate Opcode : 1011 XX RTL : undefined Flags set : undefined

This instruction’s function is not defined, therefore, it may be modified to suit processing requirements. However, this functionality is limited by the ALU’s hardware and the instruction format as implemented in the assembler. Not implemented.

Xop2

Example : xop2 rb 1 Addressing mode : immediate Opcode : 1100 RTL : undefined Flags set : undefined

This instruction’s function is not defined, therefore, it may be modified to suit processing requirements. However, this functionality is limited by the ALU’s hardware and the instruction format as implemented in the assembler. Not implemented.

Xop3

Example : xop3 rb 1 Addressing mode : immediate Opcode : 1101 RTL : undefined Flags set : undefined

This instruction’s function is not defined, therefore, it may be modified to suit processing requirements. However, this functionality is limited by the ALU’s hardware and the instruction format as implemented in the assembler. Not implemented.

Add

Example : add ra rb Addressing mode : register Opcode : 1111 + 00110 RTL : RX <- RX + RY Flags set : Z,C,O,P,N

Add 16bit source general purpose register to destination general purpose register. Not implemented. Higher and lower opcode values as defined in figure 2. In this example RX is register RA and RY is register RB, therefore, if RA=20 and RB=10 at the end of the execution phase register RA=30.

Sub

Example : sub ra rb Addressing mode : register Opcode : 1111 + 00111 RTL : RX <- RX - RY Flags set : Z,C,O,P,N

Subtract 16bit source general purpose register from destination general purpose register. Not implemented. Higher and lower opcode values as defined in figure 2. In this example RX is register RA and RY is register RB, therefore, if RA=25 and RB=10 at the end of the execution phase register RA=15.

And

Example : and ra rb Addressing mode : register Opcode : 1111 + 01000 RTL : RX <- RX & RY Flags set : Z,C,O,P,N

Perform bitwise AND on 16bit source and destination general purpose registers. Not implemented. Higher and lower opcode values as defined in figure 2. In this example RX is register RA and RY is register RB, therefore, if RA=15 and RB=7 at the end of the execution phase register RA=7.

Or

Example : or ra rb Addressing mode : register Opcode : 1111 + 01001 RTL : RX <- RX | RY Flags set : Z,C,O,P,N

Perform bitwise OR on 16bit source and destination general purpose registers. Not implemented. Higher and lower opcode values as defined in figure 2. In this example RX is register RA and RY is register RB, therefore, if RA=15 and RB=7 at the end of the execution phase register RA=15.

Xor

Example : or ra rb Addressing mode : register Opcode : 1111 + 01010 RTL : RX <- RX | RY Flags set : Z,C,O,P,N

Perform bitwise XOR on 16bit source and destination general purpose registers. Not implemented. Higher and lower opcode values as defined in figure 2. In this example RX is register RA and RY is register RB, therefore, if RA=15 and RB=7 at the end of the execution phase register RA=8.

Xop4

Example : xop4 ra rb Addressing mode : register Opcode : 1111 + 01101 RTL : undefined Flags set : undefined

This instruction’s function is not defined, therefore, it may be modified to suit processing requirements. However, this functionality is limited by the ALU’s hardware and the instruction format as implemented in the assembler. Not implemented.

Xop5

Example : xop5 ra rb Addressing mode : register Opcode : 1111 + 01110 RTL : undefined Flags set : undefined

This instruction’s function is not defined, therefore, it may be modified to suit processing requirements. However, this functionality is limited by the ALU’s hardware and the instruction format as implemented in the assembler. Not implemented.

Xop6

Example : xop6 ra rb Addressing mode : register Opcode : 1111 + 01111 RTL : undefined Flags set : undefined

This instruction’s function is not defined, therefore, it may be modified to suit processing requirements. However, this functionality is limited by the ALU’s hardware and the instruction format as implemented in the assembler. Not implemented.

Xop7

Example : xop7 ra rb Addressing mode : register Opcode : 1111 + 10000 RTL : undefined Flags set : undefined

This instruction’s function is not defined, therefore, it may be modified to suit processing requirements. However, this functionality is limited by the ALU’s hardware and the instruction format as implemented in the assembler. Not implemented.

Xop8

Example : xop8 ra rb Addressing mode : register Opcode : 1111 + 10001 RTL : undefined Flags set : undefined

This instruction’s function is not defined, therefore, it may be modified to suit processing requirements. However, this functionality is limited by the ALU’s hardware and the instruction format as implemented in the assembler. Not implemented.

Xop9

Example : xop9 ra rb Addressing mode : register Opcode : 1111 + 10010 RTL : undefined Flags set : undefined

This instruction’s function is not defined, therefore, it may be modified to suit processing requirements. However, this functionality is limited by the ALU’s hardware and the instruction format as implemented in the assembler. Not implemented.

Common programming constructs

IF Variable = Constant

Pseudo Code Assembler code Notes

IF A=0 start: variable A is stored in register

THEN test RA 0xFF RA and is 8bits. Variable B is

B = 10 jumpz zero stored in RB and is 8bits.

ELSE notZero:

B = 20 move rb 20

END IF jump exit

zero:

move rb 10

exit:

jump exit

IF Variable = Variable

Pseudo Code Assembler code Notes

IF A=B start: variable A is stored in register

THEN cmp RA 100 RA, variable B is stored in M[100]

C = 10 jumpz equal and variable C is stored in M[101]

ELSE notEqual:

C = 20 move RA 20

END IF store RA 101

jump exit

equal:

move RA 10

store RA 101

exit:

jump exit

IF Variable < Variable

Pseudo Code Assembler code Notes

IF A<B start: variable A is stored in register

THEN cmp RA 100 RA, variable B is stored in M[100]

C = 10 jumpn less and variable C is stored in M[101]

ELSE greater:

C = 20 move RA 10

END IF store RA 101

jump exit

less:

move RA 20

store RA 101

exit:

jump exit

FOR Loop

Pseudo Code Assembler code Notes

FOR I in {0..4} start: variable I is stored in

DO move RD 4 register RD and variable A

A = A + 1 move RA 0 in register RA. Loop count is

DONE loop: an 8bit value.

and RD 0xFF

jumpz exit

add RA 1

sub RD 1

jump loop

exit:

jump exit

WHILE Loop

Pseudo Code Assembler code Notes

WHILE (A<10) start: variable RA stored in register

DO move RA 0 RA and is an 8bit value.

A = A + 1 loop:

DONE cmp RA 10

jumpz exit

add RA 1

jump loop

exit:

jump exit

VARIABLES

Pseudo Code Assembler code Notes

A = 100 start: move instruction limited to a

B = 1000 move RA 0x64 signed/unsigned 8bit values. Variables A

C = 10000 moveh RB 0x03 and B are stored in registers

D = 65535 or RB 0xE8 RA and RB. Variables C and D

moveu RC 0x27

asl RC

asl RC

asl RC

asl RC

asl RC

asl RC

asl RC

asl RC

add RC 0x10

store RC C

exit:

jump exit

C:

.data 0

D:

.data 0xFFFF

This work is licensed under a Creative Commons Attribution-NonCommercial-NoDerivatives 4.0 International License.

Contact email: mike@simplecpudesign.com